## **Boolean Logic Continued**

Prof. James L. Frankel Harvard University

Version of 5:14 PM 31-Jan-2023 Copyright © 2023, 2021, 2017, 2016 James L. Frankel. All rights reserved.

| D | Clk | R                | S                |

|---|-----|------------------|------------------|

| Х | 0   | $\sim S_0 = R_0$ | $\sim R_0 = S_0$ |

| D | 1   | D                | ~D               |

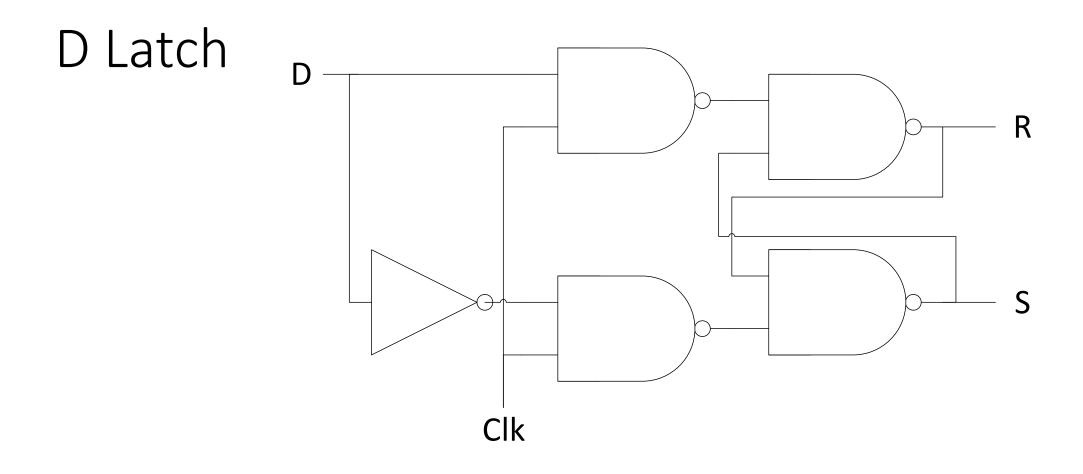

### D Latch Observations

- Because of the inversion caused by the NAND gates to D and ~D, the state of R is the same as D and the state S is the complement of D

- In D Latches, we often refer to R as Q

- And, we refer to S as ~Q

## Timing Considerations

- Time is required for an output of a gate to reflect its state after inputs change

- For any one family of logic gates, this time is simplified and referred to as a gate delay

- That is, one gate delay is the time that any primitive gate takes to produce a stable output after inputs change

- The symbol tau, **τ**, is used to refer to the gate delay

## D Latch Constraints

- Clk should be low when D changes

- Before Clk goes high, D should be stable for at least one  $\tau$

- We refer to this time as the **setup time** or **t**<sub>su</sub>

- D should not change when Clk is high

- In addition, D should not change for some time after Clk goes low

- We refer to this time as the **hold time** or **t**<sub>h</sub>

- Clk should be high until Flip Flop is stable

- One τ for (Clk NAND D) to propagate to Flip Flop inputs

- A second  $\tau$  for Flip Flop inputs to propagate to R and S

- A third  $\tau$  for outputs to propagate to the cross-coupled NAND gate inputs

- Therefore, Clk should be high for at least 3  $\tau$

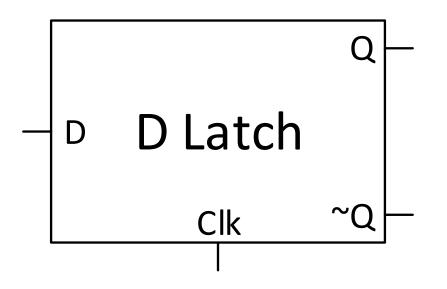

#### Encapsulation of D Latch

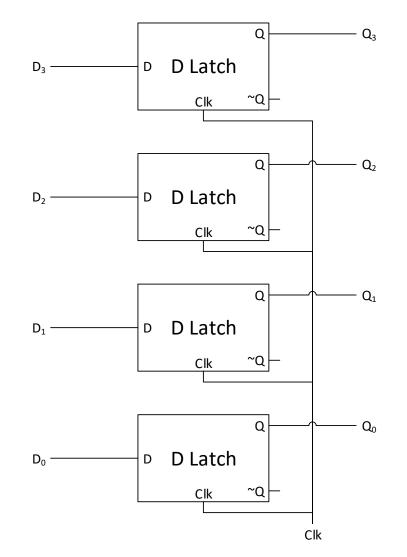

#### Four-bit Register Built from D Latches

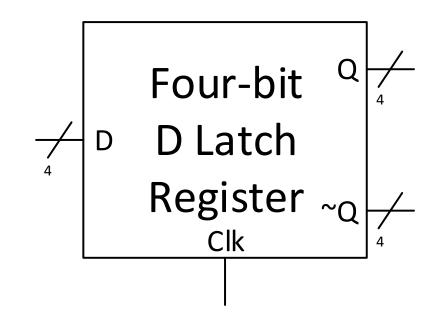

#### Encapsulation of D Latch Four-bit Register

## D Latch Register Encapsulation Observations

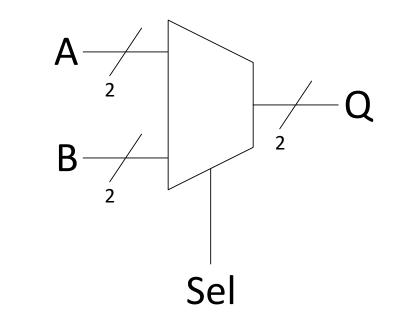

- The slashes on wires to the D Latch Register Encapsulation indicate the **bus width**

- This simplifies the diagram by collapsing replicated inputs or outputs

- In Visio, the **bus width** symbol is available under Engineering → Electrical Engineering → Transmission Paths → Bus width

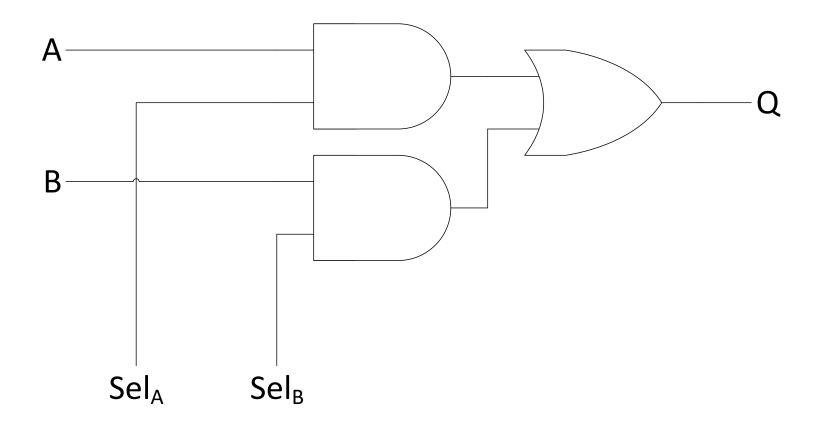

## Multiplexer, Mux, or Data Selector – Initial

• A multiplexer selects one of multiple inputs to be the output

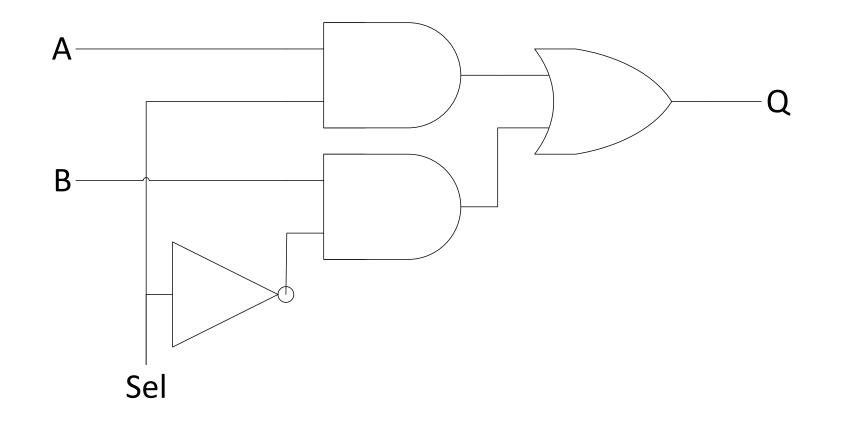

## Multiplexer, Mux, or Data Selector

- Design on previous slide also allows ORing the inputs together

- Often, there is no need to be able to OR inputs

- And, this design requires multiple Sel inputs

- So, we can use a single *Sel* input to select one of two inputs as follows

#### Multiplexer, Mux, or Data Selector – Final

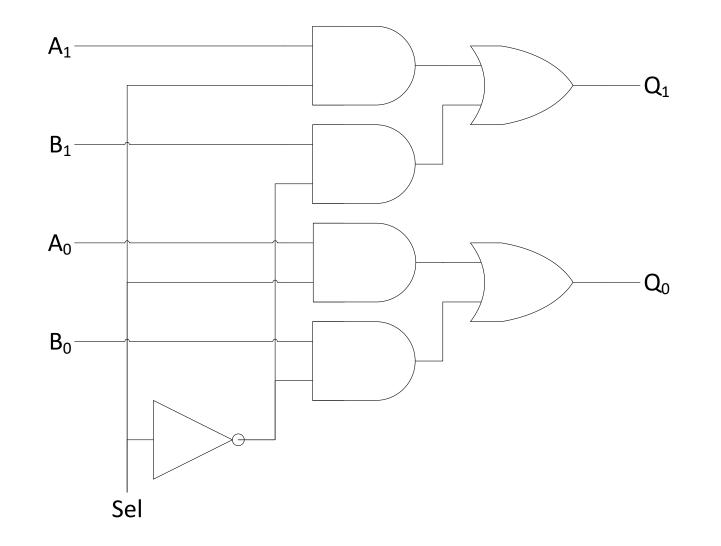

### Two-bit Mux

## Mux Encapsulation

## Open-Collector Output

- A device with an open-collector output will pull its output low when the output would be 0, but otherwise appears to be disconnected from the output

- This disconnected state is really a high impedance state signified by Z

- Devices with open-collector outputs *can* have their outputs connected together

- Thus, when several devices with open-collector outputs have their outputs connected together, any one (or more than one) of those device(s) can pull the output low

- An external device must be used to default the connected outputs to be high when no open-collector output is pulling the output low

- Typically, this is a resistor

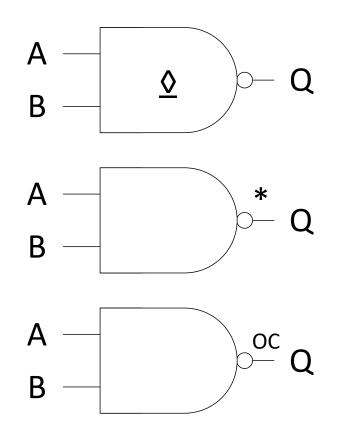

#### **Open-Collector Schematic Symbols**

## Truth Table for Open-Collector NAND Gate

| А | В | Q |

|---|---|---|

| 0 | 0 | Z |

| 0 | 1 | Z |

| 1 | 0 | Z |

| 1 | 1 | 0 |

## **Open-Collector Output Observations**

- Of course, any gate can have an open-collector output

- There is a limit to the number of devices with open-collector outputs whose outputs can be connected together

- Open-collector circuits are often called "active-low wired-OR" or "active-high wired-AND"

- Why?

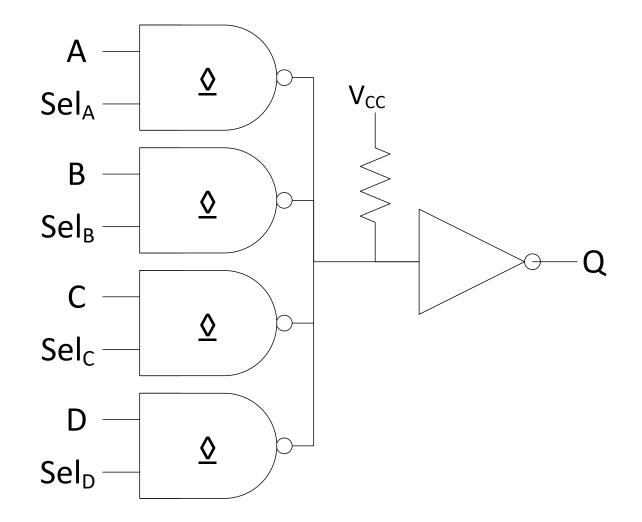

## Implementing a Bus Using Open-Collector Output Devices

- A bus is a wire that allows any one of several signals to be driven onto it

- Thus, it functions as a mux, but is implemented as a wire

- It may be driven by open-collector outputs

- Implements a mux, but doesn't require as many gates

#### **Open-Collector Bus**

## Open-Collector Devices on our Altera FPGA

- The bad news is that, alas, our Altera FPGA does not have any opencollector devices

- Therefore, we can't use them in our designs

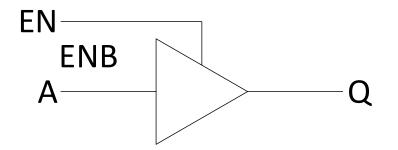

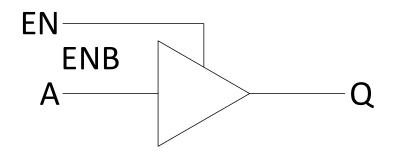

### Tri-State Output Devices

- Another device that can be used to directly implement a bus is a device with a tri-state output

- These devices are able to drive their outputs either high or low *or* place their output into a high impedance state

- The output is put into a high impedance state using an additional enable input

- Devices with tri-state outputs can have their outputs connected together, but must be carefully managed

#### Tri-State Buffer or Driver

| А | EN | Q |

|---|----|---|

| Х | 0  | Z |

| 0 | 1  | 0 |

| 1 | 1  | 1 |

# Simplified Truth Table for Tri-State Buffer or Driver

| EN | Q |

|----|---|

| 0  | Z |

| 1  | А |

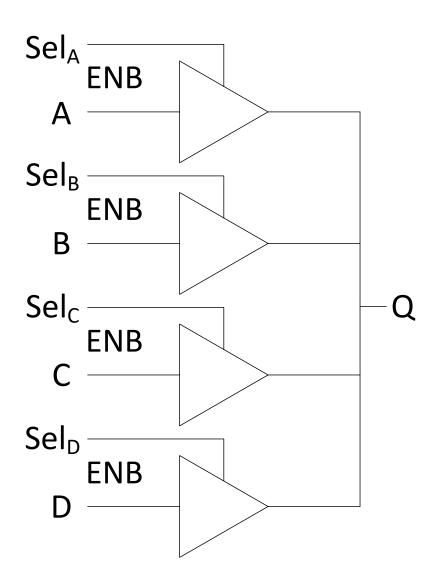

#### Tri-State Bus

## Tri-State Output Device Observations

- Because a tri-state device will drive its output either high or low if it is enabled,

- Never, never, never enable more than one tri-state device driving the same wire

- The previous circuit was potentially dangerous

- What if more than one *Sel* line was asserted?

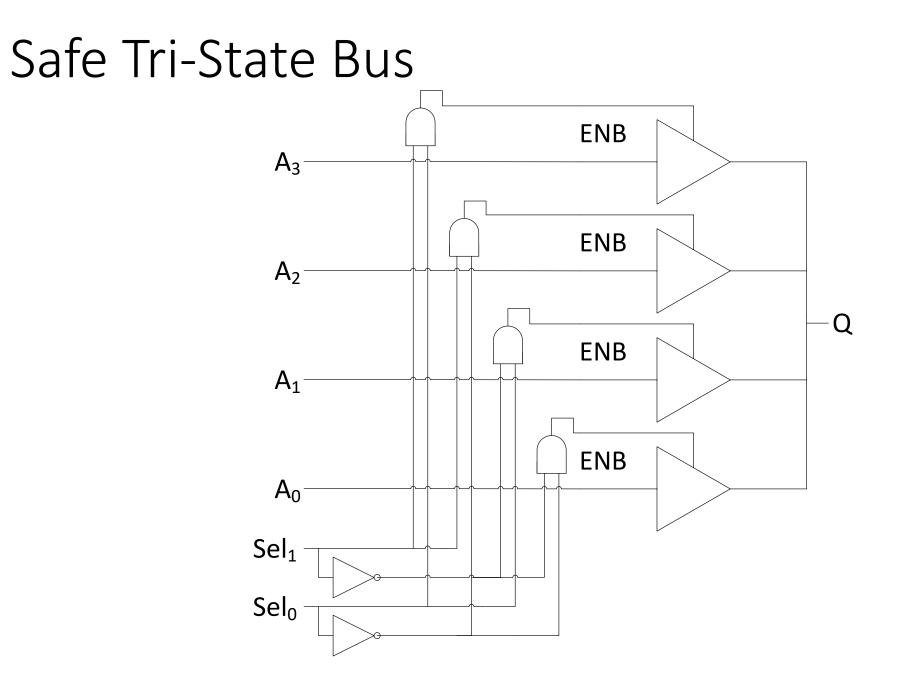

- We make sure that this can never happen by building devices that use tri-state drivers with circuitry that selects only one enable line at a time for tri-states that drive the same wire

#### Truth Table for Safe Tri-State Bus

| A <sub>3</sub> | A <sub>2</sub> | A <sub>1</sub> | A <sub>0</sub> | Sel <sub>1</sub> | Sel <sub>o</sub> | Q |

|----------------|----------------|----------------|----------------|------------------|------------------|---|

| Х              | Х              | Х              | 0              | 0                | 0                | 0 |

| Х              | Х              | Х              | 1              | 0                | 0                | 1 |

| Х              | Х              | 0              | Х              | 0                | 1                | 0 |

| Х              | Х              | 1              | Х              | 0                | 1                | 1 |

| Х              | 0              | Х              | Х              | 1                | 0                | 0 |

| Х              | 1              | Х              | Х              | 1                | 0                | 1 |

| 0              | Х              | Х              | Х              | 1                | 1                | 0 |

| 1              | Х              | Х              | Х              | 1                | 1                | 1 |

## Simplified Truth Table for Safe Tri-State Bus

| Sel <sub>1</sub> | Sel <sub>o</sub> | Q              |

|------------------|------------------|----------------|

| 0                | 0                | A <sub>0</sub> |

| 0                | 1                | A <sub>1</sub> |

| 1                | 0                | A <sub>2</sub> |

| 1                | 1                | A <sub>3</sub> |

# Further Simplified Truth Table for Safe Tri-State Bus

| Sel <sub>10</sub> | Q              |

|-------------------|----------------|

| 0                 | A <sub>o</sub> |

| 1                 | A <sub>1</sub> |

| 2                 | A <sub>2</sub> |

| 3                 | A <sub>3</sub> |

## Tri-State Devices on our Altera FPGA

- The bad news is that, alas, our Altera FPGA does not have any tri-state devices

- Therefore, we can't use them in our designs

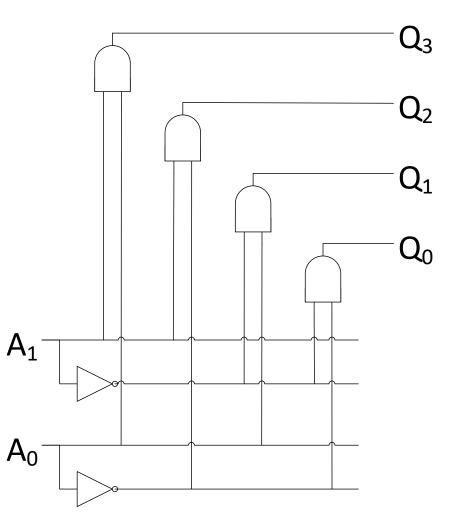

#### Decoder

- A decoder asserts one of multiple outputs based on an input binary number

- We used one in our Safe Tri-State Bus

- Here is a truth table for a 2-to-4 line decoder

| A <sub>1</sub> | A <sub>0</sub> | Q₃ | Q <sub>2</sub>   | <b>Q</b> <sub>1</sub> | Q <sub>0</sub> |

|----------------|----------------|----|------------------|-----------------------|----------------|

| 0              | 0              | 0  | 0<br>0<br>1<br>0 | 0                     | 1              |

| 0              | 1              | 0  | 0                | 1                     | 0              |

| 1              | 0              | 0  | 1                | 0                     | 0              |

| 1              | 1              | 1  | 0                | 0                     | 0              |

#### Decoder Schematic

#### **Decoder Encapsulation**